# **Switch Optimisation Theme**

# **Underpinning Power Electronics 2017**

P.M. Gammon<sup>1</sup>, P.A. Mawby<sup>1</sup>, N. Lophitis<sup>2</sup>, N. Wright<sup>3</sup>, A. O'Neill<sup>3</sup> and F. Udrea<sup>4</sup>

#### Introduction

Silicon carbide (SiC) N-channel IGBTs have the potential to revolutionise new and highly efficient ultrahigh voltage (10 kV+) applications such as HVDC, enabling a low carbon society. However, to date, only four research groups worldwide have reported on their successful development, due to the considerable challenge associated with their fabrication.

The aim of the Switch Optimisation theme of Underpinning Power Electronics is to be amongst the first groups in Europe, and the world, to develop these devices, to push the boundaries of what has been achieved in this fledgling field to date.

#### The Team

This theme brings together the UK's leading institutions in SiC device development. Within the Devices Theme of the first three years of UPE, Newcastle, Cambridge and Warwick successfully worked together to develop a SiC MOSFET process as well as working on the optimisation of Si trench IGBTs, work that underpins the development in this project.

Warwick will lead the consortium, as well as leading the Materials Development activities using their unique SiC epitaxy facilities. Cambridge will lead the Device Simulation activities, given over 20 years of experience optimising wide bandgap power devices. Newcastle will lead the Device Fabrication activities, given a history of developing novel SiC device solutions. Coventry will lead the Device Testing activities, being home to specialist HV power device equipment. Coventry will contribute to the simulation.

#### **Innovation**

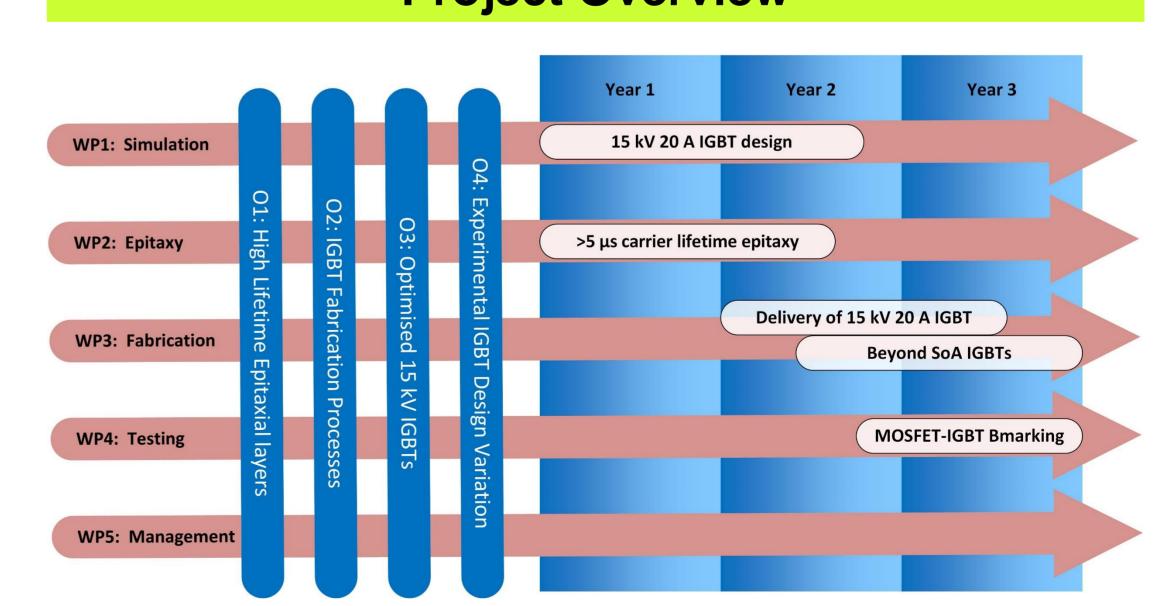

The first two years of the project will be dedicated to the development of a 15 kV SiC IGBT to rival those already produced [1,2]. Once the complex fabrication processes are in place, there is significant room for innovation.

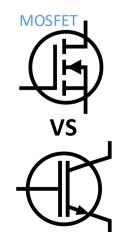

#### SiC IGBT Vs MOSFET Benchmarking

Lower voltage (5-10 kV) IGBTs with high lifetime will be developed in order to benchmark their performance against similar voltage MOSFETs. This will help establish the switch over voltage for SiC.

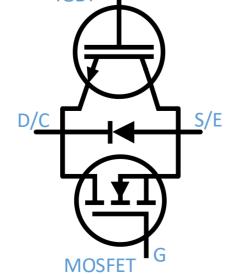

#### **An Integrated SiC MOSFET-IGBT**

Alternate P+/N+ contacts on the backside, will reintroduce unipolar action, allowing a low turn-on voltage for the IGBT. It will also reintroduce a reverse conducting diode.

**Trench Gated IGBT** – A tough challenge!

#### References

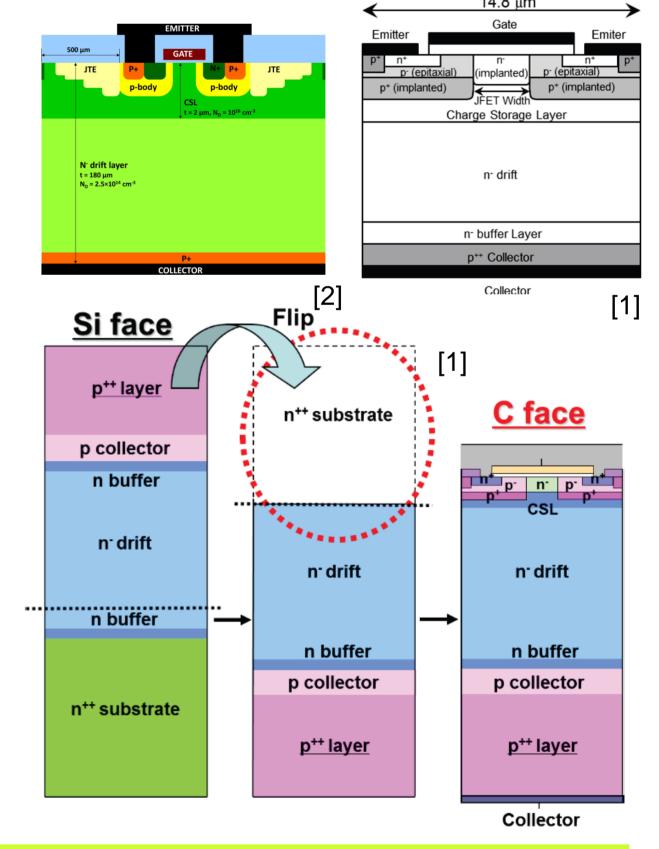

[1] Y. Yonezawa et al "Low Vf and highly reliable 16 kV ultrahigh voltage SiC flip-type n-channel implantation and epitaxial IGBT," in 2013 IEEE International Electron Devices Meeting, 2013, pp. 6.6.1-6.6.4.

[2] S. Chowdhury et al, "4H-SiC n-Channel Insulated Gate Bipolar Transistors on (0001) and (000-1) Oriented Free-Standing N-Substrates," IEEE Electron Device Letters, vol. 37, pp. 317-320, 2016.

## **Applications and Demand**

# High Power Traction Grid connected Renewables at 11kV HVDC converters

The aim of the project is to position the UK at the forefront of the emerging ultra-high voltage (5-30 kV) bipolar SiC device market. Devices at this voltage, particularly N-channel SiC IGBTs, are considered an enabling technology for microgrids, HVDC, renewables and medium voltage drives given the size and poor efficiency of current Si solutions. Such high voltage devices eliminate the need for series-connected or multi-level converter topologies and hence save energy lost to snubbers or voltage and power balancing.

### Background and the SiC IGBT Problem

10kV+ N-channel SiC IGBTs are considered the ultimate challenge in SiC device fabrication due to the need for P+ type starting SiC wafers, which are currently unavailable.

The processing challenge originates from the unavailability of a SiC P+ substrate. Hence, all the epitaxial layers needed to form an IGBT, including a 50-200 µm N- drift region, must be epitaxially grown. After this, the N+ handle wafer is removed by grinding and CMP polishing, before the front side, almost identical to a MOSFET can be fabricated.

To date, only four research groups worldwide have demonstrated an n-channel IGBT.

## **Project Overview**