# Optimal Gate Commutated Thyristor Design for Bi-mode Gate Commutated Thyristors Underpinning High, Temperature Independent, Current Controllability

Lophitis, N, Antoniou, M, Vemulapati, UR, Vobecky, J, Badstuebner, U, Stiasny, T, Wikstrom, T, Rahimo, MT & Udrea, F

Author post-print (accepted) deposited by Coventry University's Repository

# Original citation & hyperlink:

Lophitis, N, Antoniou, M, Vemulapati, UR, Vobecky, J, Badstuebner, U, Stiasny, T, Wikstrom, T, Rahimo, MT & Udrea, F 2018, 'Optimal Gate Commutated Thyristor Design for Bi-mode Gate Commutated Thyristors Underpinning High, Temperature Independent, Current Controllability' IEEE Electron Device Letters, Vol. 39, No. 9, 09.2018, p. 1342-1345.

https://dx.doi.org/10.1109/LED.2018.2847050

DOI 10.1109/LED.2018.2847050

ISSN 0741-3106 ESSN 1558-0563

Publisher: IEEE

© 2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Copyright © and Moral Rights are retained by the author(s) and/ or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This item cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder(s). The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

This document is the author's post-print version, incorporating any revisions agreed during the peer-review process. Some differences between the published version and this version may remain and you are advised to consult the published version if you wish to cite from it.

# Optimal Gate Commutated Thyristor Design for Bimode Gate Commutated Thyristors Underpinning High, Temperature Independent, Current Controllability

N. Lophitis, M. Antoniou, U. Vemulapati, J. Vobecky, U. Badstuebner, T. Wikstroem, T. Stiasny, M. Rahimo, and F. Udrea

Abstract—The Bi-mode Gate Commutated Thyristor (BGCT) is an advanced reverse conducting device aiming high power applications. Due to the high degree of interdigitation of diode parts and Gate Commutated Thyristor (GCT) parts, it is necessary to investigate how to best separate the two and at the same time, how to maximise the individual power handling capability. This work underpins the latter, for the GCT part. In achieving that, this letter details the optimisation direction, identifies the design parameters that influence the Maximum Controllable Current (MCC) and thereafter introduces a new design attribute, the "pzone". This new design not only improves the MCC at high temperature, but also at low temperature, yielding temperature independent current handling capability and at least 1000 A, or 23.5 % of improvement compared to the state-of-the-art. As a result, the proposed design constitutes an enabler for optimally designed bi-mode devices rated at least 5000 A for applications with the highest power requirement.

Index Terms— Full Wafer Modelling, Reverse Conducting, Gate Commutated Thyristor, Maximum Controllable Current, MCC.

### I. INTRODUCTION

High power applications and systems such as industrial Medium Voltage Drives (MVD), wind-power conversion systems, STATCOMs and railway interties are better served by silicon bipolar devices because of the high voltage, high current handling capability and low on state losses. The Integrated Gate Commutated Thyristor (IGCT) has become the device of choice for the above-mentioned systems due to its optimal performance, high reliability and the ease by which it can be tailored to meet the specific operating requirements set by the application. Recently proposed innovations further improved the state-of-the-art IGCTs. These include improvements aiming further increase of the current handling capability [1]–[3] and voltage rating [4], [5] or to increase the operating junction temperature of the device [2].

The Reverse Conducting IGCT (RC-IGCT) allowed the reduction of component count in Voltage Source Inverters [6]. The BGCT [7] is an advanced reverse conducting technology which aptitudes superior device characteristics [7], [8]. It features a high degree of interdigitation of GCT and diode segments. The BGCT was experimentally verified on 38 mm [8] and 91 mm wafers [9]. The neo design approach for BGCTs

proposed in [10] supersedes the conventional design optimization methodology for the MCC [11]. It comprises a "less than full" GCT cathode segment placed in the proximity of the diode separation to terminate the GCT part. It additionally improves the MCC and minimises the on-state losses. The effectiveness of the HPT+ technology on BGCTs and the impact of shallow diode anodes on the MCC was investigated in [12] but not on the neo BGCTs.

The procedure to maximise the controllable current requires a progressive and systematic failure analysis. Starting from a reference design, the MCC is quantified and the location and mechanism of failure is analysed. In this letter, the design parameters influencing the MCC are identified at first, which subsequently leads to the introduction of a new design feature, the p-zone, and to an optimal BGCT design. The proposed optimal BGCT with p-zone yields very high, and temperature independent MCC. It indeed underpins the development of large area (91 mm in diameter) 4.5 kV BGCTs with current rating larger than 5000 A, which was previously impossible.

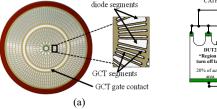

Fig. 1. The 4.5kV 91mm Bi-mode GCT wafer device (a) and the BGCT wafer model (b)

#### II. METHODOLOGY

To compare device design solutions and to assess the MCC performance, we performed failure analysis with a complex mixed mode Technology Computer Aided Design (TCAD) model that was previously developed and validated [10]–[12]. It includes a model for the wafer device but also the external circuit and gate unit. A 91 mm BGCT wafer device is depicted in Fig. 1a. The model for the wafer device is depicted in Fig. 1b. It is mixed-mode, it consists of two Finite Element Method (FEM) cells, which interconnect with SPICE wires and compact circuit components. To attain the failure and therefore the MCC, starting from low on-state current, every successful turnoff is followed by another turn off simulation at increased current level, until a failure to turn off is recorded. During these,

Manuscript received on.

N. Lophitis is with the Faculty of Engineering, Environment and Computing, Coventry University, Coventry CV1 5FB, UK (e-mail: n.lophitis @coventry.ac.uk) and also with the Electrical Engineering Department, University of Cambridge, Cambridge CB3 0FA, UK.

M. Antoniou, and F. Udrea are with the Electrical Engineering Department, University of Cambridge, Cambridge CB3 0FA, U.K. UK.

U. R. Vemulapati, and U. Badstuebner are with the ABB Switzerland Ltd., Corporate Research, Segelhofstrasse 1K, 5405 Baden-Dättwil, Switzerland. J. Vobecky, T. Wikstroem, T. Stiasny and M. Rahimo are with the ABB Switzerland Ltd., Semiconductors, CH-5600 Lenzburg, Switzerland.

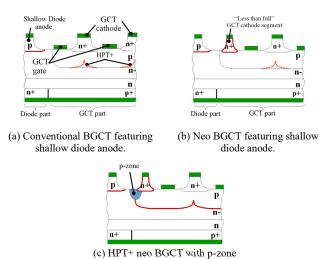

Fig. 2. Schematic structures of BGCT half-cells.

the DC-link voltage is kept constant at 2.7 kV.

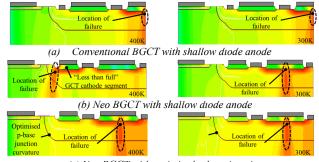

Two BGCT structure types are considered. The conventional BGCT, where the GCT part is optimised for high MCC in the conventional way [11] (Fig. 2a) and the neo BGCT [10] (Fig. 2b) with a "less than full" GCT cathode segment terminating the GCT part. The "less than full" segment is chosen to be about <sup>3</sup>/<sub>4</sub> of the full GCT cathode segment width. This is the maximum "less than full" cathode finger size to maintain the predicted merits of the neo design [10]; it therefore serves as the limiting case. The impact of varying GCT p-base junction curvature and that of HPT+ junction on the MCC is then analysed. The HPT+ structured p-base junction for the conventional BGCT and the neo BGCT is illustrated with dotted lines in Fig. 2. A new design, the p-zone HPT+ neo BGCT is then introduced (Fig. 2c) to maximise the achievable MCC.

#### III. DESIGN PARAMETERS INFLUENCING THE MCC

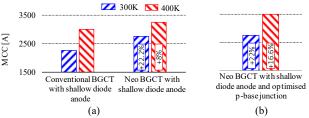

Neo design with shallow diode anode

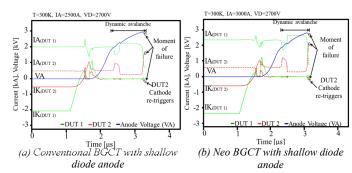

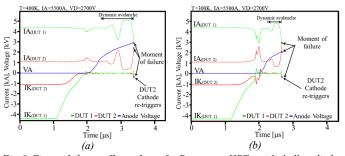

The shape of p-base junction that terminates the GCT part can affect the field concentration locally and can potentially induce lower current turn-off capability. This is more prominent when shallow diodes and neo design is adopted. The current handling capability of the neo BGCT with shallow diode anode is compared to the conventionally optimized BGCT in Fig. 3a. As shown, the MCC is higher, both at room and high temperature. The first to fail turn-off waveforms are depicted in Fig. 4. The failure mechanism of the neo BGCT with shallow diode anode (Fig. 4b) is identical to that of the conventional BGCT with shallow diode (Fig. 4a). However, the failure to turn off occurs at higher current. As shown, both fail due to the parasitic re-triggering of the "region to turn off last" and it is induced by dynamic avalanche. They are indeed in accordance to the GCT failure mechanism explained in detail in [13] and

Fig. 3. MCC results (last pass) for conventional and neo BGCT (non HPT+) designs at T=300 K and 400 K.

Fig. 4. First to fail turn off waveforms at 300 K. DUT1 corresponds to "region to turn off last" and DUT2 to the "bulk" parts of model depicted in Fig. 1b.

[14]. Fig. 5 depicts the current density contours at the moment of turn-off failure for the "region to turn off last". It reveals the location of failure within the "region to turn off last" of the BGCT. For the conventional BGCT with shallow diode anode it is always the central cathode that fails (Fig. 5a), whereas for the neo BGCT the location of failure (Fig. 5b) changes with increasing temperature. At 400 K, the "less than full" cathode fails whereas at 300 K the full-sized segment fails. With increasing temperature, the junction voltage reduces. This makes the far edge of the "less than full" cathode segment more vulnerable to retriggering. Despite that, the neo BGCT preserves the advantage of the MCC compared to the conventional design also when shallow diode anodes are comprised, something that has been shown for the first time.

# The effect of GCT p-base junction curvature

The junction curvature can be modified by moving the aluminium implantation edge progressively towards the diode side whilst keeping the boron implantation area unaltered. The MCC performance of a design that meets the above-mentioned characteristic, is shown in Fig. 3b. It achieves higher MCC at 400 K but equal room temperature performance. The current density contours depicted in Fig. 5c show that the location of failure moved from the terminating segment to the middle ones also at 400 K. Without a doubt, the results show that the shape of the p-base junction at the edge can strongly affect the final current capability of the neo design.

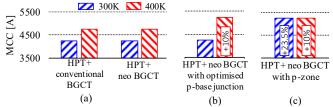

# High Power Technology for further increase of power

The implementation of HPT+ junctions can be done through an additional aluminium implantation, masked around the GCT cathode regions. Because of the additional implantation involved, multiple variations can be achieved when altering one aluminium implantation area independently to the other. Fig. 6a summarises the MCC simulation results for structures with

(c) Neo BGCT with optimised p-base junction

Fig. 5. Current density contours at the instance of turn-off failure

HPT+. When compared to those of Fig. 3, a step-increase is achieved, both for the conventional BGCT and the neo BGCT. However, the neo design with HPT+ does not offer any additional MCC advantage when compared to the conventional BGCT with HPT+.

The MCC advantage of the neo BGCTs over conventional BGCTs is attributed to the wider plasma spread in the drift region during GCT operation which reduces the impact ionization at the middle of the GCT part. With a "less than full" cathode segment being 3/4 full-segment wide, the effective width (defined as the distance carriers cover when travelling laterally under the cathode towards the gate), is up to 1/4 longer than the effective width of a full segment. That is the maximum width that maintains the merits of neo design if conventional pbase/drift junction is utilised. HPT+ profoundly alters the Efield distribution and reduces the susceptibility of all cathodes to latch-up, also when the neo design is adopted. This explains why a higher turn-off current becomes possible with HPT+. Under these conditions of higher operating current however, the longer effective width and the associated asymmetry in the base resistance of neo segments becomes more impactful. As such, the added advantage of neo design associated with the wider plasma spread becomes less effective, which is why the neo BGCT with HPT+ offers no added MCC advantage when compared to the conventional BGCT with HPT+.

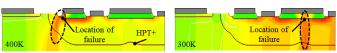

With an optimised p-base junction curvature, an increase at high temperature is achieved, but no improvement at 300 K. The result is depicted in Fig. 6b. Further, the current density contours at the instance of failure, Fig. 7a, show that at 400 K, it is the "less than full" terminating segment that fails whereas, at 300 K, it is the centremost segment that fails.

The p-zone, a new design feature to maximize the current controllability and achieve temperature independent MCC

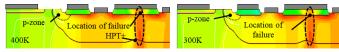

An optimised local p-zone has been introduced at the far end of the "less than full" GCT cathode. A schematic illustration of this is shown in Fig. 2c. The MCC performance of the HPT+ neo BGCT with p-zone is depicted in Fig. 6c whereas the current density contours during failure are shown in Fig. 7b. As shown, the "less than full" segment is no longer the weak point. The location of failure moves to the middle segment at 400 K, whereas at 300 K, a high increase in MCC is achieved.

The p-zone reduces the resistivity locally, counters the effect of longer effective cathode width and enhances the extraction of holes from the proximity of the neo cathode during turn-off, both at low and high temperature. The result is that the current path under the neo-cathode becomes more efficient, which means for the same current, the relative amount of current under the neo segment increases and the relative amount flowing under the middle segments reduces. This is true both at high

Fig. 6. MCC results (last pass) for HPT+ designs, including all the "neo HPT+" variants. The MCC improvement of in bars is with respect to HPT+ concentional BGCT.

(a) Neo HPT+ design with shallow diode anode

(b) P-zone neo HPT+ with shallow diode anode

Fig. 7. Current density contours at the instance of turn-off failure

Fig. 8. First to fail turn off waveforms for P-zone neo HPT+ with shallow diode anode at (a) T=300K and (b) T=400K

temperature and low temperature. At lower temperature though, the reduction of the relative amount of current flowing under the middle segment is more impactful because it is enhanced by the multiplying factor of stronger impact ionization. The consequence of a reduced current crowding in the middle finger, means avalanche induced re-triggering at the middle finger does not occur until up-to a higher turn-off current.

The first to fail turn-off waveforms are depicted in Fig. 8. The failure mechanism still identifies as dynamic avalanche induced GCT cathode re-triggering but at least 5250 A are turned off before a failure is recorded, both at 300 K and 400 K. Indeed, the p-zone allows the neo design concept to be utilised fully, also when boosted by the HPT+ technology. At T= 300 K up to 1000 A (23.5 %) higher MCC can be achieved resulting to a temperature independent current controllability.

#### IV. CONCLUSIONS

In this work, the GCT part of the BGCT was optimised for maximizing the possible current handling capability and subsequently a new design feature was introduced, the p-zone, to further increase the MCC and to enable temperature independent current handling capability. In all variants modelled and simulated, the diode part of the device featured shallow anodes. To achieve maximisation of the achievable MCC, the curvature of the p-base junction at the edge of the GCT part and the effectiveness of HPT+ were optimised. This work showed that the neo BGCT is a better choice than the conventional BGCT, also when shallow diode anodes are used. Further, it was shown that with the incorporation of the HPT+, at 400 K, the neo BGCT can lose the advantage over the conventional design, however the introduction of p-zone, can resolve this issue. Indeed, neo BGCTs with HPT+ and p-zone can achieve the highest possible MCC. Notably this MCC does not change with temperature and it is at least 1000 A (23.5%) more than the state-of-the-art. Therefore, it enables reverse conducting devices rated at least 5000 A for applications with the highest power requirement.

#### REFERENCES

- [1] N. Lophitis, M. Antoniou, F. Udrea, I. Nistor, M. Arnold, T. Wikstrom, J. Vobecky, and M. Rahimo, "The Stripe Fortified GCT: A new GCT design for maximizing the controllable current," *Proc. 2014 IEEE 26th Int. Symp. Power Semicond. Devices IC's*, pp. 123–126, Jun. 2014. doi:10.1109/ISPSD.2014.6855991

- [2] M. Arnold, T. Wikstroem, Y. Otani, and T. Stiasny, "High Temperature Operation of HPT + IGCTs," *Proc. PCIM Eur. 2011; Int. Exhib. Conf. Power Electron. Intell. Motion, Renew. Energy Energy Manag.*, May 2011

- [3] T. Wikström, M. Alexandrova, V. Kappatos, C. Winter, E. Tsyplakov, M. Mohan, and M. Chen, "94 mm Reverse-Conducting IGCT for High Power and Low Losses Applications," Proc. PCIM Asia 2017; Int. Exhib. Conf. Power Electron. Intell. Motion, Renew. Energy Energy Manag., pp. 118–123, Jun. 2017

- [4] S. Bernet, E. Carroll, P. Streit, O. Apeldoorn, P. Steimer, and S. Tschirley, "10 kV IGCTs," *IEEE Ind. Appl. Mag.*, vol. 11, no. 2, pp. 53–61, Mar. 2005. doi:10.1109/MIA.2005.1405827

- [5] I. Nistor, T. Wikstrom, and M. Scheinert, "IGCTs: High-Power Technology for power electronics applications," *Proc. 2009 IEEE Int. Semicond. Conf.*, pp. 65–73, Oct. 2009. doi:10.1109/SMICND.2009.5336607

- [6] S. Linder, S. Klaka, E. C. M. Frecker, and H. Zeller, "A new range of reverse conducting gate-commutated thyristors for high voltage, medium power applications," *Proc. 7th Eur. Conf. Power Electron. Appl.*, pp. 1117–1124, Sep. 1997

- [7] U. Vemulapati, M. Bellini, M. Arnold, M. Rahimo, and T. Stiasny, "The concept of Bi-mode Gate Commutated Thyristor-A new type of reverse conducting IGCT," *Proc. 2012 24th IEEE Int. Symp. Power Semicond. Devices ICs*, pp. 29–32, Jun. 2012. doi:10.1109/ISPSD.2012.6229015

- [8] U. Vemulapati, M. Arnold, M. Rahimo, J. Vobecky, T. Stiasny, N. Lophitis, and F. Udrea, "An experimental demonstration of a 4.5 kV Bi-mode Gate Commutated Thyristor (BGCT)," 2015 IEEE 27th Int. Symp. Power Semicond. Devices IC's, pp. 109–112, May 2015. doi:10.1109/ISPSD.2015.7123401

- [9] T. Stiasny, M. Arnold, U. R. Vemulapati, M. Rahimo, J. Vobecky, C. Kähr, and N. Hoffmann, "Experimental results of a Large Area (91mm) 4.5kV 'Bi mode Gate Commutated Thyristor' (BGCT)," Proc. PCIM Eur. 2016; Int. Exhib. Conf. Power Electron. Intell. Motion, Renew. Energy Energy Manag., 2016

- [10] N. Lophitis, M. Antoniou, U. Vemulapati, M. Arnold, I. Nistor, J. Vobecky, M. Rahimo, F. Udrea, U. Vemulapati, M. Arnold, I. Nistor, J. Vobecky, and M.

- Rahimo, "New Bi-Mode Gate-Commutated Thyristor Design Concept for High-Current Controllability and Low ON-State Voltage Drop," *IEEE Electron Device Lett.*, vol. 37, no. 4, pp. 467–470, Apr. 2016. doi:10.1109/LED.2016.2533572

- [11] N. Lophitis, M. Antoniou, F. Udrea, U. Vemulapati, M. Arnold, I. Nistor, J. Vobecky, and M. Rahimo, "Improving Current Controllability in Bi-Mode Gate Commutated Thyristors," *IEEE Trans. Electron Devices*, vol. 62, no. 7, pp. 2263–2269, Jul. 2015. doi:10.1109/TED.2015.2428994

- [12] N. Lophitis, M. Antoniou, F. Udrea, U. Vemulapati, M. Arnold, M. Rahimo, and J. Vobecky, "4.5 kV Bi-mode Gate Commutated Thyristor design with High Power Technology and shallow diode-anode," 2016 28th Int. Symp. Power Semicond. Devices ICs, pp. 371–374, Jun. 2016. doi:10.1109/ISPSD.2016.7520855

- [13] N. Lophitis, M. Antoniou, F. Udrea, F. D. Bauer, I. Nistor, M. Arnold, T. Wikstrom, and J. Vobecky, "The Destruction Mechanism in GCTs," *IEEE Trans. Electron Devices*, vol. 60, no. 2, pp. 819–826, Feb. 2013. doi:10.1109/TED.2012.2235442

- [14] N. Lophitis, M. Antoniou, F. Udrea, I. Nistor, M. Arnold, T. Wikstrom, and J. Vobecky, "Experimentally validated three dimensional GCT wafer level simulations," 2012 24th Int. Symp. Power Semicond. Devices ICs, pp. 349–352, Jun. 2012. doi:10.1109/ISPSD.2012.6229093